# PCM-MIO-A-1

16 Channel, 16-bit Analog Inputs 8 Channel, 12-bit Analog Outputs, and 48 Digital I/O

## **Product Manual**

## **Revision History**

| Document<br>Version | Last Updated<br>Date | Brief Description of Change                                       |

|---------------------|----------------------|-------------------------------------------------------------------|

| v1.0                | 8/27/20              | Initial release                                                   |

| v1.1                | 7/29/2025            | Updated Conformal Coating, added Warranty link, updated all links |

## **Copyright and Trademarks**

Copyright 2020, WINSYSTEMS, Inc.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of WINSYSTEMS, Inc. The information in the document is subject to change without notice. The information furnished by WINSYSTEMS, Inc. in this publication is believed to be accurate and reliable. However, WINSYSTEMS, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. WINSYSTEMS, Inc. makes no warranty of merchantability or fitness for any purpose. WINSYSTEMS, Inc. assumes no responsibility for any errors that may appear in this document.

## **Trademark Acknowledgments**

WINSYSTEMS is a registered trademark of WINSYSTEMS, Inc.

PC/104 is a trademark of the PC/104 Consortium.

SoftSpan is a trademark of Linear Technology Corporation.

All other marks are the property of their respective companies.

## **Table of Contents**

| 1 | Befo | re You    | Begin                                | 5    |

|---|------|-----------|--------------------------------------|------|

|   | 1.1  |           | ıgs                                  |      |

| 2 | Intr | oductio   | n                                    | 5    |

| 3 | Fund | tionalit  | hy                                   | 5    |

|   | 3.1  |           | /O Address                           |      |

|   | 3.2  | _         | pts                                  |      |

|   | 3.3  |           | -to-Digital                          |      |

|   | 3.4  | _         | -to-Analog                           |      |

|   |      | J         | ·                                    |      |

| 4 | Feat | ures      |                                      | 7    |

| 5 | Gen  | eral On   | eration                              | 8    |

|   | 5.1  | _         | n Block Diagram                      |      |

|   |      | •         | •                                    |      |

| 6 | Spe  | cificatio | ns                                   | 8    |

| 7 | Con  | figurati  | on                                   | . 10 |

|   | 7.1  | Compo     | nent Layout                          | 10   |

|   |      | 7.1.1     | Top View                             | . 10 |

|   | 7.2  | Jumpe     | r Reference                          |      |

|   |      | 7.2.1     | J7 - Base I/O Address Jumpers        |      |

|   | 7.3  | 7.2.2     | J10 - Digital I/O VCC Enable Jumpers |      |

|   | 7.3  |           | J2 - ADC Analog Input Header         |      |

|   |      | 7.3.1     | J1, J3 - D/A Analog Output Headers   |      |

|   |      | 7.3.3     | J8, J9 Digital I/O Headers           |      |

|   |      | 7.3.4     | J5, J6 - PC/104 Connectors           | . 16 |

| 8 | Soft | ware S    | ummary                               | . 17 |

|   | 8.1  |           | onverters                            |      |

|   |      | 8.1.1     | A/D1 - Starting at BASE +0           | . 17 |

|   |      | 8.1.2     | A/D2 - Starting at BASE +4           |      |

|   |      | 8.1.3     | Command Register                     | . 19 |

|    |      | 8.1.4          | Multiplexer Channel Selection        | . 19 |

|----|------|----------------|--------------------------------------|------|

|    | 8.2  | D/A Co         | onverters                            |      |

|    |      | 8.2.1          | D/A1 - Starting at BASE +8           | . 22 |

|    |      | 8.2.2          | D/A2 - Starting at BASE +12          |      |

|    |      | 8.2.3          | Command Register                     |      |

|    |      | 8.2.4          | Command Codes                        |      |

|    |      | 8.2.5          | Address Codes                        |      |

|    |      | 8.2.6          | Span Codes                           |      |

|    |      | 8.2.7<br>8.2.8 | Readback Enable                      |      |

|    |      | 8.2.9          | D/A Interrupts  D/A Examples         |      |

|    | 8.3  |                |                                      |      |

|    | 0.5  | U              |                                      |      |

|    |      | 8.3.1<br>8.3.2 | Register Definitions (WS16C48 Logic) |      |

|    |      | 8.3.2          | Register Details                     | . 28 |

| 9  | Acce | ssories        |                                      | . 30 |

|    |      |                |                                      |      |

| 10 | Soft | ware D         | rivers                               | . 30 |

| A  | Best | Practic        | es                                   | . 31 |

| •  |      |                |                                      |      |

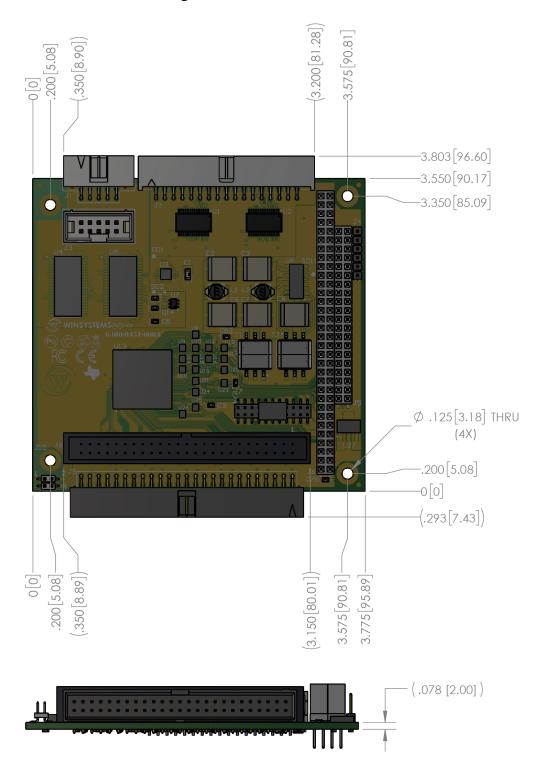

| B  | Mec  | hanical        | Drawings                             | . 35 |

| (  | War  | ranty li       | nformation                           | 36   |

## 1. Before You Begin

Review the warnings in this section and the best practice recommendations (see "Best Practices" on page 31) when using and handling the WINSYSTEMS PCM-MIO-A-1 board. Following these recommendations provides an optimal user experience and prevents damage. Read through this document and become familiar with the PCM-MIO-A-1 before proceeding.

APPLYING CONFORMAL COATING AFTER PURCHASE WILL VOID YOUR WARRANTY. FAILING TO COMPLY WITH THESE BEST PRACTICES MAY DAMAGE THE PRODUCT AND VOID YOUR WARRANTY.

## 1.1 Warnings

Only qualified personnel should configure and install the PCM-MIO-A-1. While observing best practices, pay particular attention to the following.

#### Avoid Electrostatic Discharge (ESD)

Only handle the circuit board and other bare electronics when electrostatic discharge (ESD) protection is in place. Having a wrist strap and a fully grounded workstation is the minimum ESD protection required before the ESD seal on the product bag is broken.

## 2. Introduction

This manual provides configuration and usage information for the PCM-MIO-A-1 data acquisition module. If you still have questions, contact Technical Support at (817) 274-7553, Monday through Friday, between 8 AM and 5 PM Central Standard Time (CST).

Refer to the WINSYSTEMS website at https://www.winsystems.com/ for other accessories (including cable drawings and pinouts) that can be used with your PCM-MIO-A-1.

## 3. Functionality

The PCM-MIO-A-1 is a versatile, PC/104 analog input, analog output, and digital I/O board designed for high accuracy and high channel count analog and digital I/O. The board is based upon Linear Technology's state-of-the-art precision converters and voltage references, which require no external calibration.

## 3.1 Base I/O Address

The PCM-MIO-A-1 is I/O mapped and requires 32 sequential port addresses. The base address is jumper selectable at **J7**. Care should be taken to choose an I/O area that does not conflict with other resources in the system. The specific device locations and register offsets are discussed in more detail in "Software Summary" on page 17.

## 3.2 Interrupts

The PCM-MIO-A-1 provides flexible interrupt configuration options. Each D/A converter and 24 digital I/O lines are capable of generating an interrupt. They can be setup to use individual interrupts, a single shared interrupt, or any combination of the two. The interrupts are completely software configurable and require no jumpers or other configuration. The individual registers and configuration for each device are discussed in "Software Summary" on page 17.

The PCM-MIO-A-1 can be configured to use IRQs 3, 4, 5, 6, 7, 9, 10, 11, 12, 14, or 15 depending on availability in the system. IRQs 0, 1, 2, 8, and 13 are not supported.

## 3.3 Analog-to-Digital

The PCM-MIO-A-1 analog-to-digital conversion inputs are implemented by using two, 16-bit Linear Technology LTC-1859CG devices. The board supports up to 16 single-ended input channels, 8 differential input channels or various combinations of both. The channel configuration word selects whether an input operates in single-ended or differential mode and also selects the desired input range (0 V to 5 V, 0 V to 10 V,  $\pm$ 5 V and  $\pm$ 10 V).

The LTC-1859CG uses a successive approximation algorithm and an internal sample-and-hold circuit to convert an analog input signal to 16-bit digital data. The output is two's complement binary for bipolar mode and offset binary for unipolar mode.

## 3.4 Digital-to-Analog

The PCM-MIO-A-1 provides digital-to-analog conversion using two 12-bit Linear Technology LTC-2704 devices. These SoftSpan™ quad digital-to-analog converters (DACs) are software programmable for either unipolar or bipolar mode with specific voltage ranges on a per channel basis. Each of the 8 channels can be programmed to any one of the output ranges (0 V to 5 V, 0 V to 10 V, ±2.5 V, ±5 V, ±10 V and -2.5 V to 7.5 V).

## 4. Features

The PCM-MIO-A-1 provides the following features.

#### **Analog Input**

- Two 8-channel, 16-bit analog-to-digital (A/D) (LTC-1859CG) with sample-and-hold-circuit support

- Conversion rate: 100 Ksps max.

- Any combination of up to 16 single-ended input channels and up to 8 differential input channels

- Each channel independently programmable for input type and range

- Input ranges: 0-5 V, 0-10 V, ±5 V or ±10 V

- Input protection: ±25 V

- Supports industry-standard signal conditioners

- Programmable interrupts

#### Analog Output (not available on the PCM-MIO-A-AD-1)

- Two 4-channel, 12-bit digital-to-analog (D/A) (LTC-2704CGW-12)

- Output ranges: 0-5 V, 0-10 V, ±5 V or ±10 V, +/-2.5 V, -2.5 V to 7.5 V

- Each channel independently programmable for output type and range

- Output channels can be updated and cleared individually or simultaneously

- Interrupt I/O supported

- Supports industry-standard signal conditioners

#### Digital I/O

- 48 bidirectional lines with input, output, or output with readback (FPGA with WS16C48 compatible programmed logic)

- 12 mA sink current per line

- Ability to generate an interrupt on signal change-of state (24 bits)

- Write-protection mask register for each port

- Programmable edge polarity

#### **Power**

+5 V required, 500 mA typical

#### **Operating Temperature**

• -40°C to 85°C (-40°F to 185°F)

#### **Form Factor**

• 3.6 x 3.8 in. (90 x 96 mm)

## 5. General Operation

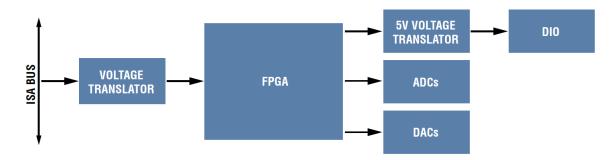

## 5.1 System Block Diagram

The PCM-MIO-A-1 utilizes a Lattice MachXO2 FPGA to communicate between the PC/104 ISA bus and the ADCs, DACs, and 48 DIO. The analog 16-bit inputs provide up to 100 Ksps, and ±25 V protection via the Linear Technology LTC1859 ADC converters. The DACs provide 12-bit outputs via the Linear Technology LTC2704.

## 6. Specifications

The PCM-MIO-A-1 adheres to the following specifications and requirements.

| Feature           | Specification                                                       |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------|--|--|--|--|--|

| Electrical        |                                                                     |  |  |  |  |  |

| V <sub>CC</sub>   | +5 V ±5% @ 500 mA (typ.), all outputs unloaded                      |  |  |  |  |  |

| Models            | PCM-MIO-A-1                                                         |  |  |  |  |  |

|                   | Includes: ADC, DAC, DIO                                             |  |  |  |  |  |

|                   | PCM-MIO-A-AD-1                                                      |  |  |  |  |  |

|                   | Includes: ADC, DIO                                                  |  |  |  |  |  |

| Absolute Maximums | A/D input protection:                                               |  |  |  |  |  |

|                   | • <b>Board off:</b> 20 k $\Omega$ input impedance, up to $\pm$ 20 V |  |  |  |  |  |

|                   | • <b>Board on:</b> 25 k $\Omega$ input impedance, up to $\pm$ 25 V  |  |  |  |  |  |

|                   | Mechanical                                                          |  |  |  |  |  |

| Dimensions        | 3.6 in x 3.8 in (90 mm x 96 mm)                                     |  |  |  |  |  |

| Weight            | 3.20 oz. (90.72 g)                                                  |  |  |  |  |  |

| PCB Thickness     | 0.078 in. (1.98 mm)                                                 |  |  |  |  |  |

| Feature                                       | Specification                                |  |  |  |  |  |

|-----------------------------------------------|----------------------------------------------|--|--|--|--|--|

|                                               | Environmental                                |  |  |  |  |  |

| Temperature                                   | -40 to +85°C (-40 to +185°F)                 |  |  |  |  |  |

| Humidity (RH) 5% to 95% non-condensing        |                                              |  |  |  |  |  |

| Mean time between failure (MTBF) <sup>a</sup> | MTBF (hours) 1074379<br>MTBF (years) 122.646 |  |  |  |  |  |

| RoHS Compliant                                | Yes                                          |  |  |  |  |  |

| Operating Systems                             |                                              |  |  |  |  |  |

| Compatible with Wind                          | ows and Linux                                |  |  |  |  |  |

a. A MTBF measurement is based on a statistical sample and is not intended to predict any one specific unit's reliability; thus MTBF is not, and should not be construed as, a warranty measurement.

## 7. Configuration

This section describes the PCM-MIO-A-1 components and configuration.

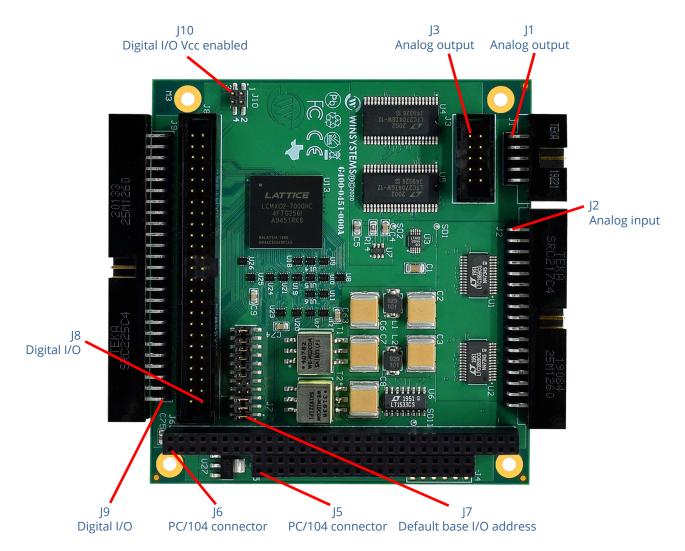

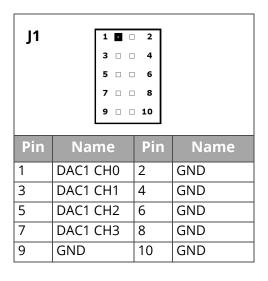

## 7.1 Component Layout

## **7.1.1 Top View**

| Item   | Description                    | Reference |

|--------|--------------------------------|-----------|

| J1, J3 | D/A Analog Output Headers      | page 13   |

| J2     | ADC Analog Input Header        | page 12   |

| J5, J6 | PC/104 Connectors              | page 16   |

| J7     | Base I/O Address Jumpers       | page 11   |

| J8, J9 | Digital I/O Headers            | page 14   |

| J10    | Digital I/O VCC Enable Jumpers | page 12   |

## 7.2 Jumper Reference

NOTE Jumper part numbers W/S# G201-0002-005 and SAMTEC 2SN-BK-G are applicable to all jumpers. These are available in a five piece kit from WINSYSTEMS (Part# KIT-JMP-G-200).

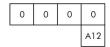

## 7.2.1 J7 - Base I/O Address Jumpers

ThePCM-MIO-A-1 is I/O mapped and requires 32 sequential port addresses. The base address is jumper selectable at **J7**. Take care to choose an I/O area that does not conflict with other resources in the system. Address bits A0 to A4 are not selectable. J7 begins at address bit A5. The specific device locations and register offsets are discussed in more detail in "Software Summary" on page 17.

#### **Layout and Pin Reference**

| Diagram | Pin   | Name |

|---------|-------|------|

|         | 1-2   | A5   |

| 1 2     | 3-4   | A6   |

| 3 4     | 5–6   | A7   |

| 5 6     | 7–8   | A8   |

| 7 🗆 8   | 9–10  | A9   |

| 9 🗆 10  | 11–12 | A10  |

| 13 14   | 13-14 | A11  |

| 15 16   | 15–16 | A12  |

| 17 18   | 17–18 | A13  |

| 19 20   | 19-20 | A14  |

| 21 22   | 21-22 | A15  |

#### Example

300HEX Default

- Jumper OPEN = 1

- Jumper INSTALLED = 0

### 7.2.2 J10 - Digital I/O VCC Enable Jumpers

#### **Layout and Pin Reference**

| Pin  | Name                                  |  |  |

|------|---------------------------------------|--|--|

|      | 1 ■ □ 3<br>2 □ □ 4                    |  |  |

| 3-4  | +5V is provided at pin 49 of J9 3-4   |  |  |

| 1-2  | +5V is provided at pin 49 of J8 1-2   |  |  |

| OPEN | No power at pin 49 of J8/J9 (default) |  |  |

#### 7.3 Connector Reference

#### 7.3.1 J2 - ADC Analog Input Header

The PCM-MIO-A-1 and PCM-MIO-A-AD-1 analog-to-digital conversion inputs are implemented by using two, 16-bit Linear Technology LTC-1859CG devices. The board supports up to 16 single-ended input channels, 8 differential input channels or various combinations of both. The channel configuration word selects whether an input operates in single-ended or differential mode and also selects the desired input range (0 V to 5 V, 0 V to 10 V,  $\pm$ 5 V, and  $\pm$ 10 V).

The LTC-1859CG uses a successive approximation algorithm and an internal sample-and-hold circuit to convert an analog input signal to 16-bit digital data. The output is two's complement binary for bipolar mode and offset binary for unipolar mode.

Programming information for the A/D controller is provided in "Software Summary" on page 17.

When the board is powered off, the A/D input has a 20 K input impedance and is protected to  $\pm 20$  V. When the board is powered on, the A/D differential channel input has a 31 K input impedance and the single-ended channel input has a 42 K input impedance. Power on inputs are protected to  $\pm 25$  V.

In differential input mode, only the even channel numbers (0, 2, 4, ...) are used and the signal is applied between the even channel number and the next odd channel input pin.

The analog input channels are terminated at **J2**. The pin definitions are shown in the illustration below.Layout and Pin Reference

| Diagram   | Pin | Name    | Pin | Name |

|-----------|-----|---------|-----|------|

|           | 1   | AD1 CH0 | 2   | GND  |

| 1 ■ □ 2   | 3   | AD1 CH1 | 4   | GND  |

| 3 🗆 🗘 4   | 5   | AD1 CH2 | 6   | GND  |

| 5 🗆 🗆 6   | 7   | AD1 CH3 | 8   | GND  |

| 7 🗆 🗆 8   | 9   | AD1 CH4 | 10  | GND  |

| 9 🗆 🗆 10  | 11  | AD1 CH5 | 12  | GND  |

| 11 □ □ 12 | 13  | AD1 CH6 | 14  | GND  |

| 13 □ □ 14 | 15  | AD1 CH7 | 16  | GND  |

| 17 □ □ 18 | 17  | AD2 CH0 | 18  | GND  |

| 19 🗆 🖸 20 | 19  | AD2 CH1 | 20  | GND  |

| 21 🗆 🗆 22 | 21  | AD2 CH2 | 22  | GND  |

| 23 🗆 🗆 24 | 23  | AD2 CH3 | 24  | GND  |

| 25 🗆 🗆 26 | 25  | AD2 CH4 | 26  | GND  |

| 27 🗆 🗆 28 | 27  | AD2 CH5 | 28  | GND  |

| 29 🗆 🗆 30 | 29  | AD2 CH6 | 30  | GND  |

| 31 □ □ 32 | 31  | AD2 CH7 | 32  | GND  |

| 33 🗆 🗆 34 | 33  | GND     | 34  | GND  |

#### **Connector**

PCB connector: TEKA SRC217C425M126-0

Mating connector: ITW-PANCON 050-034-455A

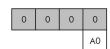

## 7.3.2 J1, J3 - D/A Analog Output Headers

NOTE The D/A converters are not available on the PCM-MIO-A-AD-1.

The PCM-MIO-A-1 provides digital-to-analog conversion output using two of the 12-bit Linear Technology LTC-2704 devices. These SoftSpan quad digital-to-analog converters (DACs) are software programmable for either unipolar or bipolar mode with specific voltage ranges on a per channel basis. Each of the 8 channels can be programmed to any one of the six output ranges (0 V to 5 V, 0 V to 10 V,  $\pm 2.5$  V,  $\pm 5$  V,  $\pm 10$  V, and -2.5 V to 7.5 V).

Programming information for the D/A controller is provided in "Software Summary" on page 17.

The analog output channels are terminated at J1 and J3. The pin definitions are shown in the illustration below.

#### **Layout and Pin Reference**

| J3       |               | 1 🗖            | □ 2      |             |

|----------|---------------|----------------|----------|-------------|

|          |               | 3 🗆            | □ 4      |             |

|          |               | <b>5</b> 🗆     | □ 6      |             |

|          |               | 7 🗆            | □ 8      |             |

|          |               | 9 🗆            | □ 10     |             |

|          |               |                |          |             |

| Pin      | Nan           | 1e             | Pin      | Name        |

| Pin<br>1 | Nan<br>DAC2 C |                | Pin<br>2 | Name<br>GND |

|          |               | НО             |          |             |

| 1        | DAC2 C        | :H0<br>:H1     | 2        | GND         |

| 1        | DAC2 C        | H0<br>H1<br>H2 | 2        | GND<br>GND  |

#### **Connector**

- PCB connector: TEKA SRC205C425M126-0 (J1), TEKA SVC205B3580135-0 (J3)

- Mating connector: ITW-PANCON 050-010-455A

## 7.3.3 J8, J9 Digital I/O Headers

The PCM-MIO-A-1 and PCM-MIO-A-AD-1 use the Lattice MachXO2 FPGA with WINSYSTEMS WS16C48 ASIC compatible programmed logic. The 48 lines are each individually programmable as input or output and the first 24 lines are capable of fully latched event sensing with edge polarity being software programmable.

The 48 lines of parallel I/O are terminated through two 50-pin connectors at **J8** and **J9**. The **J9** connector handles I/O ports 0-2 while **J8** handles ports 3-5. The pin definitions for **J8** and **J9** are shown below.

## **Layout and Pin Reference**

| Diagram                | Pin | Name | Pin | Name         |

|------------------------|-----|------|-----|--------------|

| J9                     | 50  | GND  | 49  | VCC          |

| [ <del></del>          | 48  | GND  | 47  | Port 0 Bit 0 |

| 50 🗆 🗀 49              | 46  | GND  | 45  | Port 0 Bit 1 |

| 48 🗆 🗆 47              | 44  | GND  | 43  | Port 0 Bit 2 |

| 46 🗆 🗘 45              | 42  | GND  | 41  | Port 0 Bit 3 |

| 42 🗆 🗆 41              | 40  | GND  | 39  | Port 0 Bit 4 |

| 40 □ □ 39              | 38  | GND  | 37  | Port 0 Bit 5 |

| 38 □ □ 37              | 36  | GND  | 35  | Port 0 Bit 6 |

| 36 □ □ 35              | 34  | GND  | 33  | Port 0 Bit 7 |

| 34 🗆 🗆 33              | 32  | GND  | 31  | Port 1 Bit 0 |

| 32 🗆 🗆 31              | 30  | GND  | 29  | Port 1 Bit 1 |

| 30 □ □ 29              | 28  | GND  | 27  | Port 1 Bit 2 |

| 28 🗆 🗆 27              | 26  | GND  | 25  | Port 1 Bit 3 |

| 26 □ □ 25<br>24 □ □ 23 | 24  | GND  | 23  | Port 1 Bit 4 |

| 22 🗆 🗆 21              | 22  | GND  | 21  | Port 1 Bit 5 |

| 20 🗆 🗆 19              | 20  | GND  | 19  | Port 1 Bit 6 |

| 18 🗆 🗆 17              | 18  | GND  | 17  | Port 1 Bit 7 |

| 16 🗆 🗆 15              | 16  | GND  | 15  | Port 2 Bit 0 |

| 14 🗆 🗆 13              | 14  | GND  | 13  | Port 2 Bit 1 |

| 12 🗆 🗆 11              | 12  | GND  | 11  | Port 2 Bit 2 |

| 10 🗆 🗇 9               | 10  | GND  | 9   | Port 2 Bit 3 |

| 8 🗆 🗆 7                | 8   | GND  | 7   | Port 2 Bit 4 |

| 6 🗆 🗆 5                | 6   | GND  | 5   | Port 2 Bit 5 |

| 4 □ □ 3<br>2 □ ■ 1     | 4   | GND  | 3   | Port 2 Bit 6 |

| 2 3 1                  | 2   | GND  | 1   | Port 2 Bit 7 |

|    | Diagram                | Pin | Name | Pin | Name         |

|----|------------------------|-----|------|-----|--------------|

| J8 |                        | 50  | GND  | 49  | VCC          |

| ĺг |                        | 48  | GND  | 47  | Port 3 Bit 0 |

|    | 50 🗆 🗆 49              | 46  | GND  | 45  | Port 3 Bit 1 |

|    | 48 🗆 🗆 47              | 44  | GND  | 43  | Port 3 Bit 2 |

|    | 46 □ □ 45<br>44 □ □ 43 | 42  | GND  | 41  | Port 3 Bit 3 |

|    | 42 🗆 🗆 41              | 40  | GND  | 39  | Port 3 Bit 4 |

|    | 40 🗆 🗆 39              | 38  | GND  | 37  | Port 3 Bit 5 |

|    | 38 🗆 🗆 37              | 36  | GND  | 35  | Port 3 Bit 6 |

|    | 36 □ □ 35              | 34  | GND  | 33  | Port 3 Bit 7 |

|    | 34 🗆 🗆 33              | 32  | GND  | 31  | Port 4 Bit 0 |

|    | 32 🗆 🗆 31              | 30  | GND  | 29  | Port 4 Bit 1 |

|    | 30 🗆 🗆 29              | 28  | GND  | 27  | Port 4 Bit 2 |

|    | 28 🗆 🗆 27              | 26  | GND  | 25  | Port 4 Bit 3 |

|    | 26 □ □ 25<br>24 □ □ 23 | 24  | GND  | 23  | Port 4 Bit 4 |

|    | 24 🗆 🗆 23              | 22  | GND  | 21  | Port 4 Bit 5 |

|    | 20 🗆 🗆 19              | 20  | GND  | 19  | Port 4 Bit 6 |

|    | 18 🗆 🗆 17              | 18  | GND  | 17  | Port 4 Bit 7 |

|    | 16 🗆 🗆 15              | 16  | GND  | 15  | Port 5 Bit 0 |

|    | 14 🗆 🗆 13              | 14  | GND  | 13  | Port 5 Bit 1 |

|    | 12 🗆 🗆 11              | 12  | GND  | 11  | Port 5 Bit 2 |

|    | 10 🗆 🖰 9               | 10  | GND  | 9   | Port 5 Bit 3 |

|    | 8 🗆 🗆 7                | 8   | GND  | 7   | Port 5 Bit 4 |

|    | 6 🗆 🗆 5                | 6   | GND  | 5   | Port 5 Bit 5 |

|    | 4 🗆 🗆 3<br>2 🗆 🖪 1     | 4   | GND  | 3   | Port 5 Bit 6 |

| L  | 2 1                    | 2   | GND  | 1   | Port 5 Bit 7 |

#### Connector

- PCB connector: TEKA SVC225B3580135-0 (J8), TEKA SRC225C425M126-0 (J9)

- Mating connector: ITW-PANCON 050-050-455A

## 7.3.4 J5, J6 - PC/104 Connectors

The PC/104 bus is electrically equivalent to the 16-bit ISA bus. Standard PC/104 I/O cards can be populated on PCM-MIO-A-1's connectors, located at J5 and J6. The interface does not support hot swap capability. The PC/ 104 bus connector pin definitions are provided here for reference. Refer to the PC/104 Bus Specification for specific signal and mechanical specifications.

#### **Layout and Pin Reference**

| Diagram     | Pin | Name     | Pin | Name  |

|-------------|-----|----------|-----|-------|

| J5          | D0  | GND      | C0  | GND   |

| ļ           | D1  | MEMCS16# | C1  | SBHE# |

| D0 🖬 🗆 C0   | D2  | IOCS16#  | C2  | LA23  |

| D1 - C1     | D3  | IRQ10    | C3  | LA22  |

| D2 - C2     | D4  | IRQ11    | C4  | LA21  |

| D4 □ □ C4   | D5  | IRQ12    | C5  | LA20  |

| D5 🗆 🗆 C5   | D6  | IRQ15    | C6  | LA19  |

| D6 🗆 🗆 C6   | D7  | IRQ14    | C7  | LA18  |

| D7 🗆 C7     | D8  | DACK0#   | C8  | LA17  |

| D8 = C8     | D9  | DRQ0     | C9  | MEMR# |

| D10 = = C10 | D10 | DACK5#   | C10 | MEMW# |

| D11 🗆 🗆 C11 | D11 | DRQ5     | C11 | SD8   |

| D12 🗆 🗆 C12 | D12 | DACK6#   | C12 | SB9   |

| D13 🗆 🗀 C13 | D13 | DRQ6     | C13 | SB10  |

| D14 □ □ C14 | D14 | DACK7#   | C14 | SB11  |

| D15 = C15   | D15 | DRQ7     | C15 | SB12  |

| D17 □ □ C17 | D16 | +5V      | C16 | SB13  |

| D18 🗆 🗆 C18 | D17 | MASTER#  | C17 | SB14  |

| D19 🗆 🗆 C19 | D18 | GND      | C18 | SB15  |

|             | D19 | GND      | C19 | KEY   |

| Diagram                    | Pin | Name    | Pin | Name     |

|----------------------------|-----|---------|-----|----------|

| J6                         | A1  | IOCHK#  | B1  | GND      |

|                            | A2  | SD7     | B2  | RESET    |

| A1 🖬 🗆 B1                  | A3  | SD6     | B3  | +5V      |

| A2 □ □ B2                  | A4  | SD5     | B4  | IRQ      |

| A3 □ □ B3                  | A5  | SD4     | B5  | -5V      |

| A4 □ □ B4                  | A6  | SD3     | B6  | DRQ2     |

| A6 🗆 🗆 B6                  | A7  | SD2     | B7  | -12V     |

| A7 - B7                    | A8  | SD1     | B8  | SRDY#    |

| A8 □ □ B8                  | A9  | SD0     | B9  | +12V     |

| A9 □ □ B9                  | A10 | IOCHRDY | B10 | KEY      |

| A10 🗆 🗆 B10                | A11 | AEN     | B11 | SMEMW#   |

| A11 B11                    | A12 | SA19    | B12 | SMEMR#   |

| A12 🗆 🗆 B12                | A13 | SA18    | B13 | IOW#     |

| A13 □ □ B13                | A14 | SA17    | B14 | IOR#     |

| A14 □ □ B14                | A15 | SA16    | B15 | DACK3#   |

| A15 0 0 B15                | A16 | SA15    | B16 | DRQ3     |

| A16 B16<br>A17 B17         | A17 | SA14    | B17 | DACK1#   |

| A18 B18                    | A18 | SA13    | B18 | DRQ1     |

| A19 - B19                  | A19 | SA12    | B19 | REFRESH# |

| A20 □ □ B20                | A20 | SA11    | B20 | BCLK     |

| A21 B21                    | A21 | SA10    | B21 | IRQ7     |

| A22 🗆 🗆 B22                | A22 | SA9     | B22 | IRQ6     |

| A23 □ □ B23                | A23 | SA8     | B23 | IRQ5     |

| A24 🗆 🗆 B24                | A24 | SA7     | B24 | IRQ4     |

| A25 □ □ B25                | A25 | SA6     | B25 | IRQ3     |

| A26 □ □ B26                | A26 | SA5     | B26 | DACK2#   |

| A27 □ □ B27<br>A28 □ □ B28 | A27 | SA4     | B27 | TC       |

| A28 □ □ B28                | A28 | SA3     | B28 | BALE     |

| A30 - B30                  | A29 | SA2     | B29 | +5V      |

| A31 - B31                  | A30 | SA1     | B30 | OSC      |

| A32 □ □ B32                | A31 | SA0     | B31 | GND      |

|                            | A32 | GND     | B32 | GND      |

#### **Notes:**

# = Active low signal

Rows C and D are not required on 8-bit modules.

B10 and C19 are key locations. WINSYSTEMS uses key pins as connections to GND.

Signal timing and function are as specified in ISA specification.

Signal source/sink current differ from ISA values.

#### **PCB** connectors

- TEKA PC232-A-W1A7-M (J6)

- TEKA PC220-A-W1A7-M (J5)

## 8. Software Summary

## 8.1 A/D Converters

The PCM-MIO-A-1 uses two Linear Technology LTC-1859CG 8-channel A/D converters. Each device is independently software configurable to support the listed input modes and ranges. The devices use a full-duplex serial interface which transmits and receives data simultaneously. An 8-bit command is shifted into the ADC interface to configure it for the next conversion. At the same time, the data from the previous conversion is shifted out of device. Consequently, the conversion result is delayed by one conversion from the command word.

### 8.1.1 A/D1 - Starting at BASE +0

The COMMAND register, RESOURCE register, and RESOURCE ENABLE registers are used to configure the A/D device operation. The specific options of each register are detailed here.

| Register               | Address<br>(Base+) | Read/<br>Write | 7           | 6           | 5           | 4                                   | 3                            | 2                                 | 1          | 0                                     |

|------------------------|--------------------|----------------|-------------|-------------|-------------|-------------------------------------|------------------------------|-----------------------------------|------------|---------------------------------------|

| DATA_LO                | 0                  | R              |             |             |             | LOW ORDER                           | R DATA BYTE                  |                                   |            |                                       |

|                        |                    |                | DATA-BIT 7  | DATA-BIT 6  | DATA-BIT 5  | DATA-BIT 4                          | DATA-BIT 3                   | DATA-BIT 2                        | DATA-BIT 1 | DATA-BIT 0                            |

| DATA_HI                | 1                  | R              |             |             |             | HIGH ORDER                          | R DATA BYTE                  |                                   |            |                                       |

|                        |                    |                | DATA-BIT 15 | DATA-BIT 14 | DATA-BIT 13 | DATA-BIT 12                         | DATA-BIT 11                  | DATA-BIT 10                       | DATA-BIT 9 | DATA-BIT 8                            |

| COMMAND                | 2                  | R/W            |             |             |             | COMM                                | MAND                         |                                   |            |                                       |

| (1)                    |                    |                | CMD-BIT 7   | CMD-BIT 6   | CMD-BIT 5   | CMD-BIT 4                           | CMD-BIT 3                    | CMD-BIT 2                         | CMD-BIT 1  | CMD-BIT 0                             |

| RESOURCE (2)           | 2                  | R/W            |             | DON'T       | CARE        |                                     |                              | ERRUPT ROUT<br>-3] 0, 1, 2, 8, AN |            |                                       |

|                        |                    |                | Х           | Х           | Х           | Х                                   | BIT 3                        | BIT 2                             | BIT 1      | BIT 0                                 |

| DIO<br>RESOURCE<br>(3) | 2                  | R/W            | Х           | Х           | Х           | Х                                   | BIT 3                        | BIT 2                             | BIT 1      | BIT 0                                 |

| RESOURCE               | 3                  | W              | Х           | Х           | Х           | REGISTE                             | R SELECT                     | Х                                 | Х          | INTERRUPT                             |

| ENABLE                 |                    |                |             |             |             | BIT 1                               | BIT 0                        | Х                                 | Х          | ENABLE (3)                            |

| STATUS                 | 3                  | R              | DATA READY  | Х           | Х           | INTERRUPT<br>REQUEST<br>PENDING (3) | REGISTER<br>SELECT<br>STATUS | Х                                 | Х          | INTERRUPT<br>ENABLE BIT<br>STATUS (3) |

#### **Notes:**

- (1) Accessed when REGISTER SELECT (BASE +3 bit 3) = 00

- (2) Accessed when REGISTER SELECT (BASE +3 bit 3) = 01

- (3) Accessed when REGISTER SELECT (BASE +7, bit 3) = 1X

- (4) 0=Disabled, 1=Enabled

## 8.1.2 A/D2 - Starting at BASE +4

The interface for the second A/D device is almost identical to the first device. Notice in this table that the REGISTER SELECT function within the RESOURCE ENABLE register is only a single bit. In both software examples shown below, action 1 (one) should be replaced with:

1. Write **xxxx1xxx** to bit 3 of BASE +7 (select access to Resources).

Bit 4 is a don't care in this case, so it is possible to use identical code for both devices just noting the different base address.

| Register               | Address<br>(Base+) | Read/<br>Write | 7           | 6           | 5           | 4                                   | 3                                                                          | 2           | 1          | 0                                     |  |

|------------------------|--------------------|----------------|-------------|-------------|-------------|-------------------------------------|----------------------------------------------------------------------------|-------------|------------|---------------------------------------|--|

| DATA_LO                | 4                  | R              |             |             | <u>'</u>    | LOW ORDER                           | DATA BYTE                                                                  | <u>'</u>    | <u>'</u>   |                                       |  |

|                        |                    |                | DATA-BIT 7  | DATA-BIT 6  | DATA-BIT 5  | DATA-BIT 4                          | DATA-BIT 3                                                                 | DATA-BIT 2  | DATA-BIT 1 | DATA-BIT 0                            |  |

| DATA_HI                | 5                  | R              |             |             |             | HIGH ORDER                          | R DATA BYTE                                                                |             |            |                                       |  |

|                        |                    |                | DATA-BIT 15 | DATA-BIT 14 | DATA-BIT 13 | DATA-BIT 12                         | DATA-BIT 11                                                                | DATA-BIT 10 | DATA-BIT 9 | DATA-BIT 8                            |  |

| COMMAND                | 6                  | R/W            |             |             |             | COMN                                | /AND                                                                       |             |            |                                       |  |

| (1)                    |                    |                | CMD-BIT 7   | CMD-BIT 6   | CMD-BIT 5   | CMD-BIT 4                           | CMD-BIT 3                                                                  | CMD-BIT 2   | CMD-BIT 1  | CMD-BIT 0                             |  |

| RESOURCE (2)           | 6                  | R/W            |             | DON'        | T CARE      |                                     | INTERRUPT ROUTING ASSIGNMENT<br>IRQ[15-3] 0, 1, 2, 8, AND 13 NOT AVAILABLE |             |            |                                       |  |

|                        |                    |                | Х           | Х           | Х           | Х                                   | BIT 3                                                                      | BIT 2       | BIT 1      | BIT 0                                 |  |

| DIO<br>RESOURCE<br>(3) | 2                  | R/W            | Х           | Х           | Х           | Х                                   | BIT 3                                                                      | BIT 2       | BIT 1      | BIT 0                                 |  |

| RESOURCE               | 7                  | W              | Х           | Х           | Х           | Х                                   | REGISTER                                                                   | Х           | Х          | INTERRUPT                             |  |

| ENABLE                 |                    |                |             |             |             |                                     | SELECT                                                                     | Х           | Х          | ENABLE (3)                            |  |

| STATUS                 | 7                  | R              | DATA READY  | Х           | Х           | INTERRUPT<br>REQUEST<br>PENDING (3) | REGISTER<br>SELECT<br>STATUS                                               | Х           | Х          | INTERRUPT<br>ENABLE BIT<br>STATUS (3) |  |

#### Notes:

- (1) Accessed when REGISTER SELECT (BASE +7 bit 3) = 0

- (2) Accessed when REGISTER SELECT (BASE +7 bit 3) = 1

- (3) 0=Disabled, 1=Enabled

### 8.1.3 Command Register

Each A/D device contains an 8-bit command register to configure the inputs as single-ended or differential with a desired input range of 0 V–5 V, 0 V-10 V,  $\pm 5 V$ , and  $\pm 10 V$ . The following describes the register options.

|            |          |           |          | II  | NPUT RANG | E       |        |

|------------|----------|-----------|----------|-----|-----------|---------|--------|

| 7          | 6        | 5         | 4        | 3   | 2         | 1       | 0      |

| SGL / DIFF | ODD SIGN | SELECT 1  | SELECT 0 | UNI | GAIN      | NAP     | SLEEP  |

|            | MUX CH   | ANNEL SEL | ECTION   |     |           | NOT SUP | PORTED |

### 8.1.4 Multiplexer Channel Selection

| М            | UX AI       | DDRE | SS  | DII | FFERE | NTIA | L CH | ANNE | L SEL | ECTI | NC | М            | UX AI       | DDRE | SS  | SINGLE-ENDED CHANNEL SELEC |   |   | TION | I |   |   |   |     |

|--------------|-------------|------|-----|-----|-------|------|------|------|-------|------|----|--------------|-------------|------|-----|----------------------------|---|---|------|---|---|---|---|-----|

| SGL/<br>DIFF | ODD<br>SIGN | SEL  | ECT | 0   | 1     | 2    | 3    | 4    | 5     | 6    | 7  | SGL/<br>DIFF | ODD<br>SIGN | SEL  | ECT | 0                          | 1 | 2 | 3    | 4 | 5 | 6 | 7 | СОМ |

|              | Sidiv       | 1    | 0   |     |       |      |      |      |       |      |    |              | Sidiv       | 1    | 0   |                            |   |   |      |   |   |   |   |     |

| 0            | 0           | 0    | 0   | +   | -     |      |      |      |       |      |    | 1            | 0           | 0    | 0   | +                          |   |   |      |   |   |   |   | -   |

| 0            | 0           | 0    | 1   |     |       | +    | -    |      |       |      |    | 1            | 0           | 0    | 1   |                            |   | + |      |   |   |   |   | -   |

| 0            | 0           | 1    | 0   |     |       |      |      | +    | -     |      |    | 1            | 0           | 1    | 0   |                            |   |   |      | + |   |   |   | -   |

| 0            | 0           | 1    | 1   |     |       |      |      |      |       | +    | -  | 1            | 0           | 1    | 0   |                            |   |   |      |   |   | + |   | -   |

| 0            | 1           | 0    | 0   | -   | +     |      |      |      |       |      |    | 1            | 1           | 0    | 0   |                            | + |   |      |   |   |   |   | -   |

| 0            | 1           | 0    | 1   |     |       | -    | +    |      |       |      |    | 1            | 1           | 0    | 1   |                            |   |   | +    |   |   |   |   | -   |

| 0            | 1           | 1    | 0   |     |       |      |      | -    | +     |      |    | 1            | 1           | 1    | 0   |                            |   |   |      |   | + |   |   | -   |

| 0            | 1           | 1    | 1   |     |       |      |      |      |       | -    | +  | 1            | 1           | 1    | 1   |                            |   |   |      |   |   |   | + | -   |

#### **Channel Selection**

Bits 7–4 of the command register assigns the channel configuration for the requested conversion. The converter measures the voltage between the two channels indicated by the + and - signs in the table below. In differential mode, measurements are from any of the four adjacent input pairs in either polarity. In single-ended mode, all input channels are measured with respect to GND. Both the + and - inputs are sampled simultaneously so common mode noise is rejected.

#### **Range Selection**

Bits 3 and 2 of the command register determine the input range for the conversion. Setting UNI to a logical one selects a unipolar conversion while a zero selects bipolar. The GAIN bit selects the input span for the conversion in conjunction with the UNI bit. The table below defined the selection options.

### **Input Range Selection**

| 3   | 2    |             |

|-----|------|-------------|

| UNI | GAIN | INPUT RANGE |

| 0   | 0    | ±5 V        |

| 1   | 0    | 0 V to 5 V  |

| 0   | 1    | ±10 V       |

| 1   | 1    | 0 V to 10 V |

### **Examples of Multiplexer Options**

Examples of multiplexer options and changing the MUX assignment on The fly are shown below.

| CHANNEL |      |

|---------|------|

| 0,1     | +(-) |

| 0,1     | -(+) |

| 2.2     | +(-) |

| 2,3     | -(+) |

| 4 5     | +(-) |

| 4,5     | -(+) |

|         | +(-) |

| 6,7     | -(+) |

4 Differential

| CHANNEL |        |

|---------|--------|

| 0       | +      |

| 1       | +      |

| 2       | +      |

| 3       | +      |

| 4       | +      |

| 5       | +      |

| 6       | +      |

| 7       | +      |

|         | COM(-) |

8 Single-Ended

| CHANNEL |        |

|---------|--------|

| 0,1     | +      |

| 0,1     | -      |

| 2,3     | -      |

| 2,3     | +      |

| 4       | +      |

| 5       | +      |

| 6       | +      |

| 7       | +      |

|         | COM(-) |

Combinations of Differential and Single-Ended

| CHANNEL |          |

|---------|----------|

|         |          |

| 4 5     | +        |

| 4,5     | -        |

| 6.7     | +        |

| 6,7     | -        |

|         | COM(-)   |

|         | (UNUSED) |

| 1st Co  | nversion |

CHANNEL

....

4,5

+

+

6

7 COM(-)

2nd Conversion

#### Example 1 - ADC1

The following is a polled mode example for A/D1.

| 1. Write <b>xxx00xxx</b> to bits 3 & 4 of BASE +3.                                                                                                                     | Select access to CMD              |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|

| 2. Write <b>CMD</b> selection to BASE +2.                                                                                                                              | Set MUX channel operation & range |  |  |  |  |  |

| 3. Read data from BASE +0 and discard.                                                                                                                                 | Lo_Byte unknown data              |  |  |  |  |  |

| 4. Read data from BASE +1 and discard.                                                                                                                                 | Hi_Byte unknown data              |  |  |  |  |  |

| 5. Write <b>CMD</b> selection to BASE +2 again.                                                                                                                        | Set MUX channel operation & range |  |  |  |  |  |

| 6. Read data from BASE +0.                                                                                                                                             | Lo_Byte                           |  |  |  |  |  |

| 7. Read data from BASE +1.*                                                                                                                                            | Hi_Byte                           |  |  |  |  |  |

| *The data received is actually the result of the first CMD written. Note that all readings are offset by one action due to the latching of the serial input mechanism. |                                   |  |  |  |  |  |

| 8. Additional readings are achieved by repeating steps 5 throu                                                                                                         | gh 7.                             |  |  |  |  |  |

#### Example 2 - ADC2

The following is a polled mode example for A/D2, note the difference in starting address and resource enable.

| 1. Write <b>xxxx0xxx</b> to bit 3 of BASE +7.                                                                                                                          | Select access to CMD              |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|

| 2. Write <b>CMD</b> selection to BASE +6.                                                                                                                              | Set MUX channel operation & range |  |  |  |

| 3. Read data from BASE +4 and discard.                                                                                                                                 | Lo_Byte unknown data              |  |  |  |

| 4. Read data from BASE +5 and discard.                                                                                                                                 | Hi_Byte unknown data              |  |  |  |

| 5. Write <b>CMD</b> selection to BASE +6 again. S                                                                                                                      | et MUX channel operation & range  |  |  |  |

| 6. Read data from BASE +4.                                                                                                                                             | Lo_Byte                           |  |  |  |

| 7. Read data from BASE +5.* Hi_Byte                                                                                                                                    |                                   |  |  |  |

| *The data received is actually the result of the first CMD written. Note that all readings are offset by one action due to the latching of the serial input mechanism. |                                   |  |  |  |

| 8. Additional readings are achieved by repeating steps 5 through 7.                                                                                                    |                                   |  |  |  |

NOTE Read the documentation included with the sample programs and drivers for more complex examples.

#### A/D Interrupts

To operate using interrupt mode, IRQ routing must be configured and interrupts enabled for each device. This is achieved with the Resource and Resource Enable registers. The following would apply to A/D1:

- 1. Write **xxx01xxx** to bits 4 & 3 of BASE +3 (select access to Resource Register).

- 2. Write IRQ selection (0-15 hex) to bits 3-0 of BASE +2 (xF Hex = IRQ 15).

- 3. Write **xxxxxx1** BASE +3 to enable the IRQ.

Enabling an interrupt for A/D2 can be achieved in the same manner with the appropriate offset.

It is possible for both devices to share an interrupt or use individual interrupts. When sharing interrupts, the most efficient method to

determine which device generated an interrupt request is to utilize the Master Interrupt Status Register.

## 8.2 D/A Converters

The PCM-MIO-A-1 contains two Linear Technology LTC-2704 digital-to-analog converter (DAC) devices. Each device is a 4-channel converter with software selectable output span.

### 8.2.1 D/A1 - Starting at BASE +8

The COMMAND register, RESOURCE register and RESOURCE ENABLE registers are used to configure the D/A device operation. The specific options of each register are detailed here.

| Register           | Address<br>(Base+) | Read/<br>Write | 7                    | 6          | 5           | 4                                   | 3                            | 2                             | 1           | 0                                     |            |            |  |  |

|--------------------|--------------------|----------------|----------------------|------------|-------------|-------------------------------------|------------------------------|-------------------------------|-------------|---------------------------------------|------------|------------|--|--|

| DATA_LO            | 8                  | R/W            |                      | <u>'</u>   | <u>'</u>    | LOW ORDER                           | DATA BYTE                    | <u>'</u>                      | <u>'</u>    |                                       |            |            |  |  |

|                    |                    |                | DATA-BIT 7           | DATA-BIT 6 | DATA-BIT 5  | DATA-BIT 4                          | DATA-BIT 3                   | DATA-BIT 2                    | DATA-BIT 1  | DATA-BIT 0                            |            |            |  |  |

| READBACK           | 8                  | R              |                      |            |             | LOW ORDER                           | R DATA BYTE                  |                               |             |                                       |            |            |  |  |

| (1)                |                    |                | DATA-BIT 7           | DATA-BIT 6 | DATA-BIT 5  | DATA-BIT 4                          | DATA-BIT 3                   | DATA-BIT 2                    | DATA-BIT 1  | DATA-BIT 0                            |            |            |  |  |

| DATA_HI            | 9                  | R/W            |                      |            |             | HIGH ORDER                          | R DATA BYTE                  |                               |             |                                       |            |            |  |  |

|                    |                    |                | DATA-BIT 15          | DATA-BIT14 | DATA-BIT 13 | DATA-BIT 12                         | DATA-BIT 11                  | DATA-BIT 10                   | DATA-BIT 9  | DATA-BIT 8                            |            |            |  |  |

| READBACK           | 9                  | R              | HIGH ORDER DATA BYTE |            |             |                                     |                              |                               |             |                                       |            |            |  |  |

| (1)                |                    |                |                      |            | DATA-BIT 15 | DATA-BIT 14                         | DATA-BIT 13                  | DATA-BIT 12                   | DATA-BIT 11 | DATA-BIT 10                           | DATA-BIT 9 | DATA-BIT 8 |  |  |

| COMMAND            | 10                 | 10             | 10                   | 10         | 10 R/       | R/W                                 |                              |                               |             | COMN                                  | MAND       |            |  |  |

| (2)                |                    |                | CMD-BIT 7            | CMD-BIT 6  | CMD-BIT 5   | CMD-BIT 4                           | CMD-BIT 3                    | CMD-BIT 2                     | CMD-BIT 1   | CMD-BIT 0                             |            |            |  |  |

| RESOURCE<br>(3)    | 10                 | R/W            |                      | DON'T CARE |             |                                     |                              | ING ASSIGNMI<br>ND 13 NOT AVA |             |                                       |            |            |  |  |

|                    |                    |                | X                    | Х          | Х           | X                                   | BIT 3                        | BIT 2                         | BIT 1       | BIT 0                                 |            |            |  |  |

| RESOURCE<br>ENABLE | 11                 | W              | X                    | X          | X           | READBACK<br>ENABLE                  | REGISTER<br>SELECT           | X                             | X           | INTERRUPT<br>ENABLE (4)               |            |            |  |  |

| STATUS             | 11                 | R              | DATA READY           | Х          | Х           | INTERRUPT<br>REQUEST<br>PENDING (4) | REGISTER<br>SELECT<br>STATUS | Х                             | Х           | INTERRUPT<br>ENABLE BIT<br>STATUS (4) |            |            |  |  |

#### **Notes:**

- (1) Accessed when READBACK ENABLE (BASE +11 bit 4) = 1

- (2) Accessed when REGISTER SELECT (BASE +11 bit 3) = 0

- (3) Accessed when REGISTER SELECT (BASE +11 bit 3) = 1

- (4) 0=Disabled, 1=Enabled

## **8.2.2** D/A2 - Starting at BASE +12

As shown in the table below, interface to the second device is almost identical to the first with a change in the base address.

The RESOURCE ENABLE register does contain an additional register select bit, MASTER IRQ / DA2 SELECT. If this bit is set to 1, reading BASE +15 results in the status of the Master Interrupt Status Register.

| Register               | Address<br>(Base+) | Read/<br>Write | 7           | 6                    | 5              | 4                                   | 3                                                                          | 2                   | 1                   | 0                                     |

|------------------------|--------------------|----------------|-------------|----------------------|----------------|-------------------------------------|----------------------------------------------------------------------------|---------------------|---------------------|---------------------------------------|

| DATA_LO                | 12                 | R/W            |             |                      |                | LOW ORDER                           | DATA BYTE                                                                  |                     |                     |                                       |

|                        |                    |                | DATA-BIT 7  | DATA-BIT 6           | DATA-BIT 5     | DATA-BIT 4                          | DATA-BIT 3                                                                 | DATA-BIT 2          | DATA-BIT 1          | DATA-BIT 0                            |

| READBACK               | 12                 | R              |             |                      |                | LOW ORDER                           | DATA BYTE                                                                  |                     |                     |                                       |

| (1)                    |                    |                | DATA-BIT 7  | DATA-BIT 6           | DATA-BIT 5     | DATA-BIT 4                          | DATA-BIT 3                                                                 | DATA-BIT 2          | DATA-BIT 1          | DATA-BIT 0                            |

| DATA_HI                | 13                 | R/W            |             |                      |                | HIGH ORDER                          | R DATA BYTE                                                                |                     |                     |                                       |

|                        |                    |                | DATA-BIT 15 | DATA-BIT 14          | DATA-BIT 13    | DATA-BIT 12                         | DATA-BIT 11                                                                | DATA-BIT 10         | DATA-BIT 9          | DATA-BIT 8                            |

| READBACK               | -                  |                |             | HIGH ORDER DATA BYTE |                |                                     |                                                                            |                     |                     |                                       |

| (1)                    |                    |                | DATA-BIT 15 | DATA-BIT 14          | DATA-BIT 13    | DATA-BIT 12                         | DATA-BIT 11                                                                | DATA-BIT 10         | DATA-BIT 9          | DATA-BIT 8                            |

| COMMAND                | 14                 | R/W            |             |                      | COMMAND        |                                     |                                                                            |                     |                     |                                       |

| (2)                    |                    |                | CMD-BIT 7   | CMD-BIT 6            | CMD-BIT 5      | CMD-BIT 4                           | CMD-BIT 3                                                                  | CMD-BIT 2           | CMD-BIT 1           | CMD-BIT 0                             |

| RESOURCE<br>(3)        | 14                 | R/W            |             | DON'                 | T CARE         |                                     | INTERRUPT ROUTING ASSIGNMENT<br>IRQ[15-3] 0, 1, 2, 8, AND 13 NOT AVAILABLE |                     |                     |                                       |

|                        |                    |                | Х           | Х                    | Х              | Х                                   | BIT 3                                                                      | BIT 2               | BIT 1               | BIT 0                                 |

| RESOURCE<br>ENABLE     | 15                 | W              | X           | Х                    | D/A2<br>SELECT | READBACK<br>ENABLE                  | REGISTER<br>SELECT                                                         | X                   | Х                   | INTERRUPT<br>ENABLE (4)               |

| STATUS (5)             | 15                 | R              | DATA READY  | Х                    | Х              | INTERRUPT<br>REQUEST<br>PENDING (4) | REGISTER<br>SELECT<br>STATUS                                               | Х                   | Х                   | INTERRUPT<br>ENABLE BIT<br>STATUS (4) |

| IRQ<br>REGISTER<br>(6) | 15                 | R              |             | Х                    | Х              | DA/2 IRQ<br>PENDING                 | DIO IRQ<br>PENDING                                                         | DA/1 IRQ<br>PENDING | AD/2 IRQ<br>PENDING | AD/1 IRQ<br>PENDING                   |

#### Notes:

- (1) Accessed when READBACK ENABLE (BASE +15 bit 4) = 1

- (2) Accessed when REGISTER SELECT (BASE +15 bit 3) = 0

- (3) Accessed when REGISTER SELECT (BASE +15 bit 3) = 1

- (4) 0=Disabled, 1=Enabled

- (5) Accessed when D/A2 SELECT (BASE + 15 bit 5) = 0

- (6) Accessed when D/A2 SELECT (BASE + 15 bit 5) = 1

The Linear Technology LTC-2704 devices are unique in that each channel consists of a double-buffered data register (B1 Code and B2 Code) and a double-buffered span register (B1 Span and B2 Span). B1 buffers are the holding buffers and data is loaded into each one using a write operation, the DAC outputs are not affected. The contents of the B2 buffers can only be updated by copying the contents of B1 into B2 via an update operation initiated by the Command Code. The contents of the B2 buffers (both DAC Span and DAC Code) directly control the DAC output voltage or the DAC output range. Configuration, programming and writing of the D/A data is achieved through a series of control registers listed below for each DAC.

### 8.2.3 Command Register

Each DAC contains a command register used to configure the span and load the data. The command word consists of a 4-bit command and a 4-bit address, as shown. Each DAC contains a command register used to

configure the span and load the data. The command word consists of a 4 bit command and a 4-bit address, as shown.

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| C3 | C2 | C1 | C0 | A3 | A2 | A1 | A0 |

#### 8.2.4 Command Codes

NOTE Codes not shown are reserved and should not be used.

| С3 | C2 | C1 | CO | Command                                         | Readback Point<br>Current Input Word  | Readback Pointer<br>Next Input Word |

|----|----|----|----|-------------------------------------------------|---------------------------------------|-------------------------------------|

| 0  | 0  | 1  | 0  | Write to B1 Span DAC n                          | Set by Previous Command               | B1 Span DAC n                       |

| 0  | 0  | 1  | 1  | Write to B1 Span DAC n                          | Set by Previous Command               | B1 Span DAC n                       |

| 0  | 1  | 0  | 0  | Update B1 -> B2 DAC n                           | Set by Previous Command               | B2 Span DAC n                       |

| 0  | 1  | 0  | 1  | Update B1 -> B2 All DAC n                       | Set by Previous Command               | B2 Span DAC n                       |

| 0  | 1  | 1  | 0  | Write to B1 Span DAC n Update B1 -> B2 DAC n    | Set by Previous Command B1 Span DAC n |                                     |

| 0  | 1  | 1  | 1  | Write to B1 Code DAC n Update B1 -> B2 DAC n    | Set by Previous Command B2 Span DAC n |                                     |

| 1  | 0  | 0  | 0  | Write to B1 Span DAC n Update B1 -> B2 All DACs | Set by Previous Command               | B2 Span DAC n                       |

| 1  | 0  | 0  | 1  | Write to B1 Code DAC n Update B1 -> B2 All DACs | Set by Previous Command               | B2 Span DAC n                       |

| 1  | 0  | 1  | 0  | Read B1 Span DAC n                              | B1 Span DAC n                         |                                     |

| 1  | 0  | 1  | 1  | Read B1 Code DAC n                              | B1 Span DAC n                         |                                     |

| 1  | 1  | 0  | 0  | Read B2 Span DAC n                              | B2 Span DAC n                         |                                     |

| 1  | 1  | 0  | 1  | Read B2 Code DAC n                              | B2 Span DAC n                         |                                     |

| 1  | 1  | 1  | 1  | No Operation Set by Previous Command B2 Span D  |                                       | B2 Span DAC n                       |

#### 8.2.5 Address Codes

NOTE Codes not shown are reserved and should not be used.

| A3 | A2 | A1 | A0 | n        | Readback Pointer n |

|----|----|----|----|----------|--------------------|

| 0  | 0  | 0  | 0  | DAC A    | DAC A              |

| 0  | 0  | 1  | 0  | DAC B    | DAC B              |

| 0  | 1  | 0  | 0  | DAC C    | DAC C              |

| 0  | 1  | 1  | 0  | DAC D    | DAC D              |

| 1  | 1  | 1  | 1  | All DACs | DAC A              |

## 8.2.6 Span Codes

The span for each channel is set by loading the desired value into the data registers, then issuing one of the span commands. The last 4 bits set the span as shown below. The rest of the data should be set to **0**.

NOTE Codes not shown are reserved and should not be used.

| <b>S</b> 3 | S2 | <b>S1</b> | S0 | Span                    |

|------------|----|-----------|----|-------------------------|

| 0          | 0  | 0         | 0  | Unipolar 0 V to 5 V     |

| 0          | 0  | 0         | 1  | Unipolar 0 V to 10 V    |

| 0          | 0  | 1         | 0  | Bipolar -5 V to 5 V     |

| 0          | 0  | 1         | 1  | Bipolar -10 V to 10 V   |

| 0          | 1  | 0         | 0  | Bipolar -2.5 V to 2.5 V |

| 0          | 1  | 0         | 1  | Bipolar -2.5 V to 7.5 V |

#### 8.2.7 Readback Enable

Each time a command is issued to one of Linear Technology LTC-2704 devices, the value of one of the buffers is simultaneously shifted out of the device. Except when issuing one of the specific readback commands (Ax, Bx, Cx, Dx), the data returned corresponds to the Readback Pointer from the previous command as shown in the Command Codes Table. The Readback Enable bit must be set to 1 to read this data.

NOTE If the Readback Enable bit is set to **0**, a read of the DAC data registers returns the last value written to that register not the Readback value of the actual buffers.

### 8.2.8 D/A Interrupts

To operate using interrupt mode, IRQ routing must be configured and interrupts enabled for each device. This is achieved with the Resource and Resource Enable registers. The following would apply to D/A1:

- 1. Write **xxxx1xxx** to bit 3 of BASE +11 (select access to Resource Register).

- 2. Write IRQ selection (0-15 hex) to bits 3-0 of BASE +10 (xF Hex = IRQ 15).

- 3. Write **xxxxxx1** BASE +11 to enable the IRQ.

Enabling an interrupt for D/A2 can be achieved in the same manner with the appropriate offset.

It is possible for both devices to share an interrupt or use individual interrupts. When sharing interrupts, the most efficient method to determine which device generated an interrupt request is to utilize the Master Interrupt Status Register.

## 8.2.9 D/A Examples

The most basic method is to first set the output span for a channel and then write the output value for that channel. Notice that the configuration and data write operations can each be performed with either a single or double instruction sequence. Each channel can be updated individually using command values 6Xh and 7Xh (for configuration and output data, respectively), which pre-loads the value and present it to the DAC with a

single instruction sequence. The second option is to pre-load the configuration and output data using command values 2Xh and 3Xh and then present the values to the DAC either individually (with command value 4Xh) or simultaneously (with command value 5Xh).

#### **Example 1 - Single Instruction Sequence**

To configure and write data to a DAC channel, each with a single command sequence, is very simple. The configuration must be set first and then the data output is written. Of course the span configuration is only required to be set once unless changes are required during the application.

| 1. Write <b>xxxx0xxx</b> to bit 3 of BASE +11.                             | Select access to CMD           |  |  |  |

|----------------------------------------------------------------------------|--------------------------------|--|--|--|

| 2. Write <b>Span data 0000xxxx</b> to BASE +8.                             | Where <b>xxxx</b> = Span       |  |  |  |

| 3. Write <b>00000000 (zero)</b> BASE +9.                                   | High order byte for Span       |  |  |  |

| 4. Write <b>CMD 01100xxx</b> to BASE +10.                                  | Where <b>xxx</b> = DAC channel |  |  |  |

| 5. Write <b>Low Byte data</b> to BASE +8.                                  |                                |  |  |  |

| 6. Write <b>High Byte data</b> to BASE +9.                                 |                                |  |  |  |

| 7. Write <b>CMD 01110xxx</b> to BASE +10.                                  | Where <b>xxx</b> = DAC channel |  |  |  |

| 8. Additional channels are then programmed by repeating steps 2 through 7. |                                |  |  |  |

#### **Example 2 - Double Instruction Sequence**

The second option is to pre-load the configuration and output data using command values 2Xh and 3Xh and then present the values to the DAC either individually using command value 4Xh simultaneously with command value 5Xh.

This example demonstrates pre-loading the span configuration and data output values for each DAC channel and then presenting the information simultaneously to all DAC channels.

| 1. Write <b>xxxx0xxx</b> to bit 3 of BASE +11.                   | Select access to CMD            |

|------------------------------------------------------------------|---------------------------------|

| 2. To set Span Configuration for Channel 0:                      |                                 |

| Write <b>Span Configuration data 00000000 (zero)</b> to BASE +8. | Set <b>Span</b> = 0 V to 5V     |

| Write <b>00000000 (zero)</b> to BASE +9.                         | High Order Data Byte            |

| Write <b>CMD 00100000</b> to BASE +10.                           | Move data to B1 Span            |

| 3. To set Span Configuration for Channel 1:                      |                                 |

| Write <b>Span Configuration data 00000001</b> to BASE +8.        | Set <b>Span</b> = 0 V to 10 V   |

| Write <b>00000000 (zero)</b> to BASE +9.                         | High Order Data Byte            |

| Write <b>CMD 00100010</b> to BASE +10.                           | Move data to B1 Span            |

| 4. To set Span Configuration for Channel 2:                      |                                 |

| Write <b>Span Configuration data 00000010</b> to BASE +8.        | Set <b>Span</b> = -5V to 5V     |

| Write <b>00000000 (zero)</b> to BASE +9.                         | High Order Data Byte            |

| Write <b>CMD 00100100</b> to BASE +10.                           | Move data to B1 Span            |

| 5. To set Span Configuration for Channel 3:                      |                                 |

| Write <b>Span Configuration data 00000011</b> to BASE +8.        | Set <b>Span</b> = -10 V to 10 V |

| Write <b>00000000 (zero)</b> to BASE +9.                         | High Order Data Byte            |

| Write <b>CMD 00100110</b> to BASE +10.                           | Move data to B1 Span            |

| 6. To pre-load Data Output for Channel 0:                        |                                 |

| Write <b>Low Byte data</b> to BASE +8.                           |                                 |

| Write <b>High Byte data</b> to BASE +9.        |                                       |

|------------------------------------------------|---------------------------------------|

| Write <b>CMD 00110000</b> to BASE +10.         | Move data to B1 Code                  |

| 7. To pre-load Data Output for Channel 1:      |                                       |

| Write <b>Low Byte data</b> to BASE +8.         |                                       |

| Write <b>High Byte data</b> to BASE +9.        |                                       |

| Write <b>CMD 00110010</b> to BASE +10.         | Move data to B1 Code                  |

| 8. To pre-load Data Output for Channel 2:      |                                       |

| Write <b>Low Byte data</b> to BASE +8.         |                                       |

| Write <b>High Byte data</b> to BASE +9.        |                                       |

| Write <b>CMD 00110100</b> to BASE +10.         | Move data to B1 Code                  |

| 9. To pre-load Data Output for Channel 3:      |                                       |

| Write <b>Low Byte data</b> to BASE +8.         |                                       |

| Write <b>High Byte data</b> to BASE +9.        |                                       |

| Write <b>CMD 00110110</b> to BASE +10.         | Move data to B1 Code                  |

| 10. To simultaneously update all DAC channels: |                                       |

| Write CMD 0101xxxx to BASE+10.                 | Move SPAN/DATA B1>>B2 All<br>Channels |

If the application requires all DAC channels to be configured to the same output span, command value 8Xh supports this action with a single instruction sequence. Likewise if all DAC channels are written with the same data output, then command value 9Xh both pre-loads and presents the value to all DAC channels with a single instruction sequence.

## 8.3 Registers

## 8.3.1 Register Definitions (WS16C48 Logic)

The PCM-MIO-A-1 and PCM-MIO-A-AD-1 use a Lattice MachXO2 FPGA with WINSYSTEMS WS16C48 ASIC compatible programmed logic. This provides 48 lines of digital I/O. There are 17 unique registers within the WS16C48

logic. The following table summarizes the registers, and the text that follows provides details on each of the internal registers.

| BASE+ | I/O Address Offset | Page 0    | Page 1 | Page 2 | Page 3  |

|-------|--------------------|-----------|--------|--------|---------|

| 16    | 00h                |           | Port   | 0 I/O  |         |

| 17    | 01h                |           | Port   | 1 I/O  |         |

| 18    | 02h                |           | Port   | 2 1/0  |         |

| 19    | 03h                |           | Port   | 3 I/O  |         |

| 20    | 04h                |           | Port   | 4 I/O  |         |

| 21    | 05h                |           | Port   | 5 I/O  |         |

| 22    | 06h                |           | Int_Pe | nding  |         |

| 23    | 07h                | Page/Lock |        |        |         |

| 24    | 08h                | IRQ_REG   | Pol_0  | Enab_0 | Int_ID0 |

| 25    | 09h                | REV_LO    | Pol_1  | Enab_1 | Int_ID1 |

| 26    | 0ah                | REV_HI    | Pol_2  | Enab_2 | Int_ID2 |

#### 8.3.2 Register Details

#### Port 0 through 5 I/O

Each I/O bit in each of the six ports can be individually programmed for input or output. Writing a  $\bf 0$  to a bit position causes the corresponding output pin to go to a high-impedance state (pulled high by external 10 K $\Omega$  resistors). This allows it to be used as an input. When used in the input mode, a read reflects the inverted state of the I/O pin, such that a high on the pin reads as a  $\bf 0$  in the register. Writing a  $\bf 1$  to a bit position causes that output pin to sink current (up to 12 mA), effectively pulling it low.

#### INT\_PENDING

This read-only register reflects the combined state of the  $INT_ID0$  through  $INT_ID2$  registers. When any of the lower three bits are set, it indicates that an interrupt is pending on the I/O port corresponding to the bit position(s) that are set. Reading this register allows an Interrupt Service Routine to quickly determine if any interrupts are pending and which I/O port has a pending interrupt.

#### PAGE/LOCK

This register serves two purposes. The upper two bits select the register page in use as shown here.

| D7 | D6 | Page   |

|----|----|--------|

| 0  | 0  | Page 0 |

| 0  | 1  | Page 1 |

| 1  | 0  | Page 2 |

| 1  | 1  | Page 3 |